Description

ECE 832: Analog Integrated Circuit Design was a 3-credit graduate course taught at Michigan State University for Electrical and Computer Engineering majors. The catalog description for this course is: Device modeling. Circuit simulation. Integrated circuit building blocks. Amplifiers, Noise. The co-requisite for this course is ECE 402.

The companion textbook used in this course is :

Gray, Hurst, Lewis,& Meyer, Analysis and Design of Analog Integrated Circuits, Wiley, 2001

Table of Contents

Chapter 3: Single-Transistor and Multiple-Transistor Amplifiers

3.2 Two-Port Modeling of Amplifiers

Admittance Parameters, Impedance Parameters, Hybrid Parameter, Inverse Hybrid Parameters, Circuit Representation of Two-Port Networks.

3.3 Basic Single-Transistor Amplifier Stages

Small-Signal Model of a BJT, JFET and MOSFET, Common-Emitter Configuration, Common-Source Configuration

3.4 Multiple-Transistor Amplifier Stages

Darlington Pair

3.5 Differential Pairs

Bartlett’s Bisection Theorem, Basic Differential Amplifier, Differential Gain, Common-Mode Gain, Input Resistance, Common-Mode Rejection Ratio, Current Source Biasing

Chapter 3: Supplemental Problems and Solutions

S3.1, S3.2, S3.3, S3.4, S3.5, S3.6, S3.7, S3.8, S3.9, S3.10, S3.11, S3.12, S3.13, S3.14, S3.15, S3.16

Chapter 1: Devices and SPICE Models

1.5 Large-Signal Behavior of MOSFETs

Transfer Characteristics, Shichman-Hodges Equations, SPICE Curve Tracer, Large-Signal SPICE Model, Small-Signal Model

1.3 Large-Signal Behavior of Bipolar Transistors

Transfer Characteristics, Eber-Moll Equations, Large-Signal SPICE Model, SPICE Curve Tracer, Small-Signal Model

1.X Large-Signal Behavior of JFETs

Transfer Characteristics, Device Equations, SPICE Curve Tracer, Large-Signal SPICE Model, Small-Signal Model

1.Y FET – BJT Analogy

Chapter 1: Supplemental Problems and Solutions

S1.1, S1.2, S1.3, S1.4, S1.5

Chapter 4: Current Mirror, Active Loads and References

4.2 Current Mirrors

Simple BJT Current Mirror, Model, MOSFET Current Mirror, Design and Simulation, Cascode BJT Current Mirror, Output Resistance, SPICE Verification, Cascode MOSFET Current Mirror, Design and Simulation, Swing Limits, Output Resistance, Wilson BJT Current Mirror, SPICE Verification

4.3 Active Loads

Complementary Load, Common-Emitter Amplifier, Common-Source Amplifier, Diode Connected Load – Common Source Amplifier, BJT Differential Pair with Current-Mirror Load, Operating Point, AC Differential Analysis, Symmetry, Output Resistance, Model, AC Common-Mode Analysis, Output Resistance, CMRR, Large-Signal Response, CMOS Differential Pair with Current-Mirror Load, Operating Point, AC Differential Analysis, Symmetry, Output Resistance, Model, AC Common-Mode Analysis, Output Resistance, CMRR, Large-Signal Response,

4.4 Voltage and Current References

MOSFET Voltage Divider, Design and Simulation, Biasing a Current Mirror

Chapter 4: Supplemental Problems and Solutions

S4.1, S4.2, S4.3, S4.4, S4.5, S4.6, S4.7, S4.8, S4.9, S4.10, S4.11, S4.12, S4.13, S4.14, S4.15

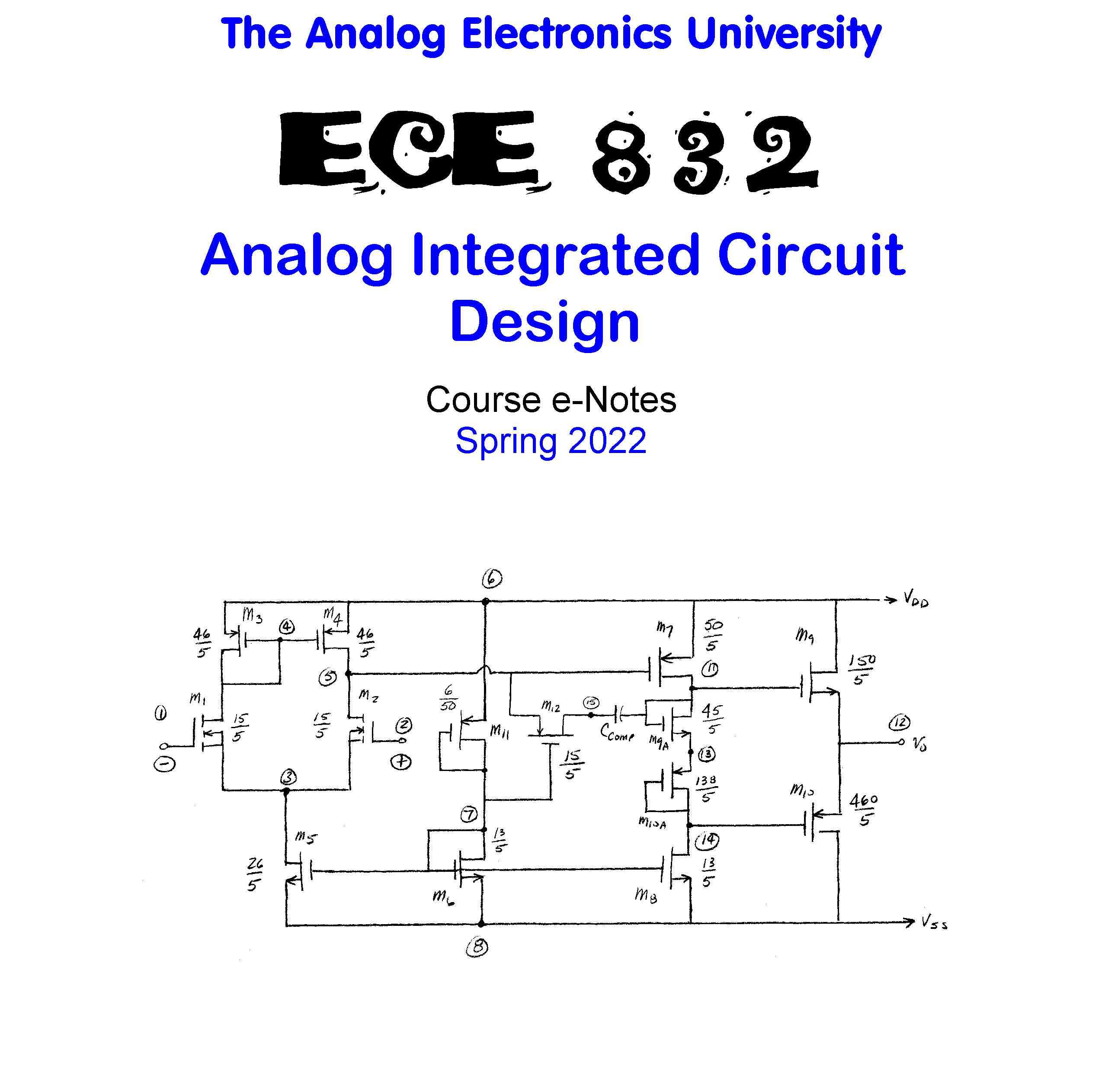

Chapter 6: Operational Amplifiers with Single-Ended Outputs

6.8 Bipolar Op-Amps – Intersil 8741 Op-Amp

Schematic, SPICE model, DC Transfer Curve, DC Operating Point – Input Stage, Intermediate Stage, Output Stage, Short Circuit Protection, Simulated Small-Signal Gain for Differential and Common-Mode Inputs Small-Signal Model – Input Stage, Intermediate Stage, Output Stage, Overall Model, Offset Adjustment, Transfer Curve with Adjustment, Output Clipping, Frequency Response with and without Dominate Pole Compensation, Stability Criterion, Step Response with and without Dominate Pole Compensation, Dominate Pole Approximation, Slew Rate, Large Signal Step Response

Chapter 7: Frequency Response of Integrated Circuits

7.X Large-Signal Model Capacitance

NMOS, PMOS, Physical Structure for CBX, C’GS,C’GD,C’GB,

NPN, PNP, LPNP

7.2 Single-Stage Amplifiers

Common-Source with Active Load – High Frequencies, Open Circuit Time Constant Approximation to Bandwidth

Chapter 9: Feedback Response and Stability of Feedback Amplifiers

9.X CMOS Op-Amp Design

Differential Amplifier Input Stage, SPICE Testing, Differential Gain, Common-Mode Gain, Small- and Large- Signal Time Domain Response, Differential DC Transfer Curve and Analysis, Common-Mode DC Transfer Curve and Analysis, Common-Source Second Stage and Analysis, Class AB Output Stage with Analysis, Modified Second Stage, Phase Margin, Buffer Instability, Adding a Dominant Pole

9.Y Characterizing the Op-Amp – Making a Virtual Data Sheet with SPICE

DC Transfer Curve, Open-Loop Gain, Output Impedance, Common-Mode Input Range, Common-Mode Gain, CMRR, Short Circuit Current, Slew Rate, Supply Current, Non-inverting Amplifier, Stability – Revisted

9.Z Analysis and Re-Design

Short Circuit Current, Origins of Slew Rate, Re-Design for Stability, Transmission Zero, Replacing the Biasing and Compensating Resistors with MOSFETs, Level 2 Model Parameters, Extracting Level 1 Parameters from Higher Level Models

Chapter 11: Noise in Integrated Circuits

11.3 Noise Models

Input Referenced Noise Model for an Op-Amp, Approximating Peak-to-Peak Noise, Approximating Input Noise using Data Sheet or SPICE Equivalent Input Noise vs Frequency Plots, Thermal Resistor Noise

11.4 Circuit Noise Calculations

Audio Frequency Inverting Amplifier, Restricting Bandwidth to Lower Noise

11.X Noise in PSpice

Noise Bandwidth, Noise Analysis in SPICE, Noise Mechanisms